芯片性能提升遭遇瓶颈

集成电路技术持续发展,过去那种每24个月单位面积内晶体管数量就翻倍的情形,现在很难达成了。这清楚地显示出当下芯片性能提升遇到了瓶颈,没办法只靠工艺技术来促使性能进步,架构创新成了关键。这种现状让全球芯片产业都体会到了巨大压力。

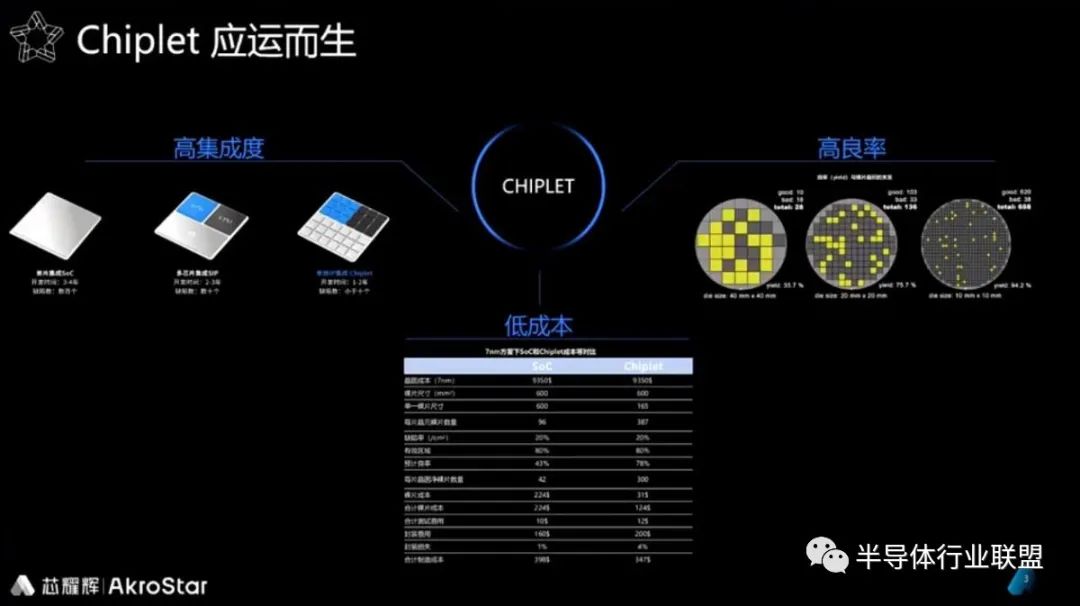

比如说,传统的单片集成SoC采用统一工艺制程,各个部分要同步迭代,开发时间需要三到四年,缺陷多达数百个,效率非常低,急需新的技术来突破这种困境,给芯片性能提升带来新方向。

Chiplet突破传统局限

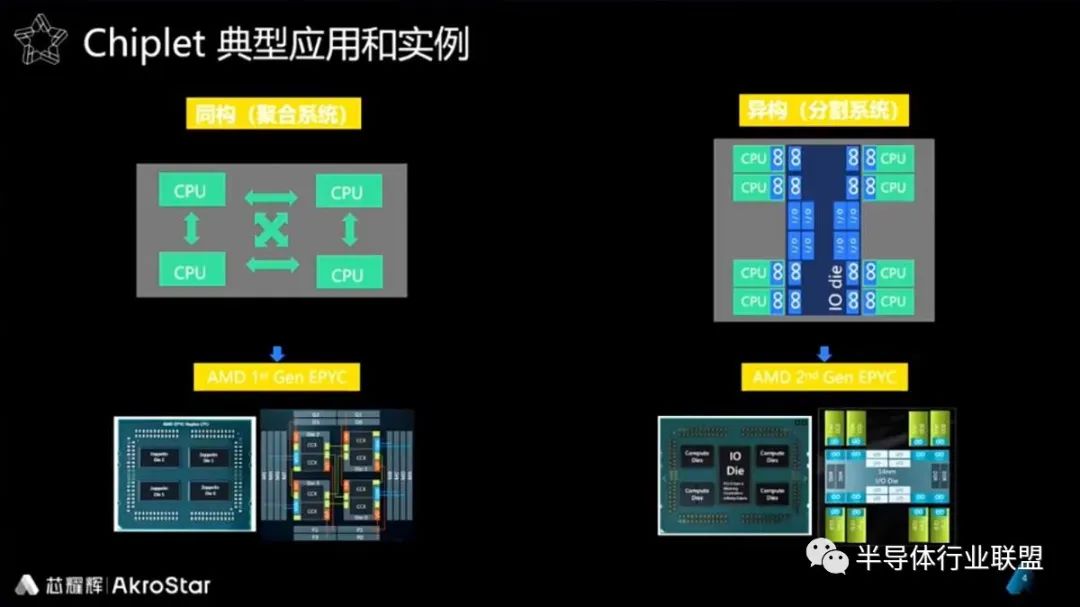

Chiplet借助多个芯片的片间集成,能突破传统单芯片的上限,还能显著提高芯片的集成度,它与传统方法差异较大,具有独特的优势。

比如把单独的IP集成到Chiplet中,把不同功能切开,对部分单元工艺进行选择性迭代,迭代裸片后快速制造出下一代产品,这大大加速了产品上市周期,能让新技术更快地惠及市场,满足各行业对芯片性能不断增长的需求。

Chiplet降低成本与提升良率

在系统级芯片设计里,模拟电路以及大功率输入输出等,对制程不敏感,它们不需要高端芯片制程。把系统级芯片中的功能模块划分成一个个单独的芯粒,针对功能去选择合适的制程,这样能够有效地让芯片实现最小化。

这样做有着极为明显的好处,它提高了芯片的良率,还大幅降低了芯片成本。在芯片产业中成本压力巨大,Chiplet技术为企业节省了大量资源,提升了企业的竞争力,推动产业更健康地发展。

Chiplet助力算力扩展

通过使用高速接口,借助先进封装技术,将多颗Die融合在一颗大芯片内,如此便能够实现算力的扩展,这种方式适用于众多产品,像CPU、FPGA、通信芯片等 。

特别是在那些对算力要求极高的领域,像人工智能、大数据处理等,Chiplet技术能够满足它们持续增长的算力需求。比如说在数据中心,借助Chiplet技术可以提高服务器的运算能力,加快数据处理的速度,使得各种复杂的计算任务能够更高效地完成。

Chiplet发展阶段与技术储备

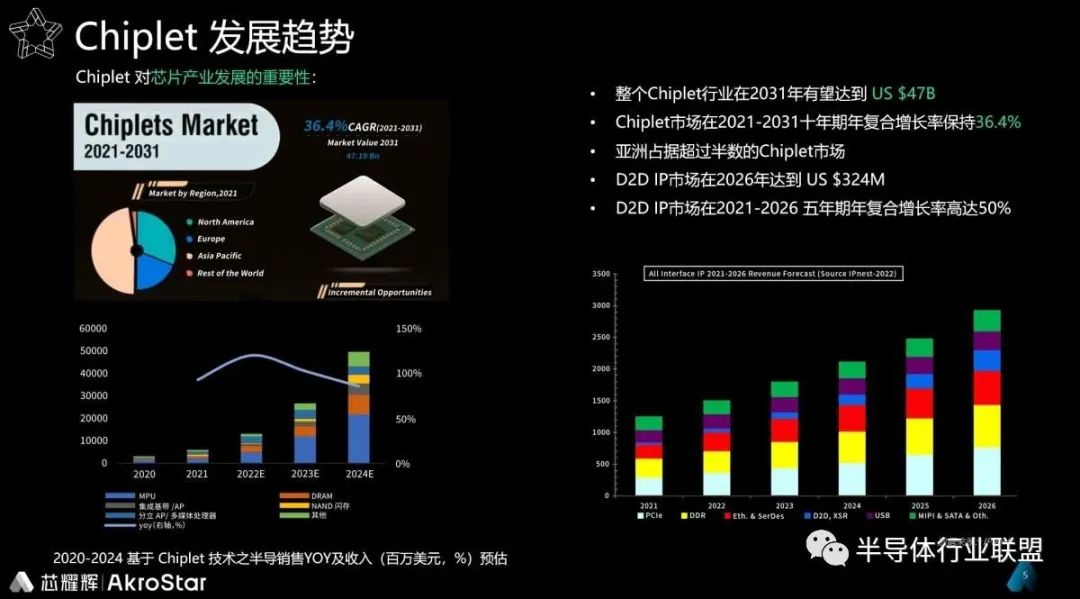

Chiplet的发展是分阶段开展的。在2023年之前的两三年,处于生态早期阶段。芯片公司会对芯片进行分拆,去寻找先进封装组合。并且各家是按照自己定义的协议来做产品的,当时还没有形成统一标准。

在这个过程里,IP供应商面临着更高的要求,他们需要具备高端芯片设计能力,还要有进行多品类IP布局的能力,以及平台化运作能力。与此同时,Intel和台积电已经拥有了相关的技术储备,它们通过中介层把多个Chiplet互连起来,并且技术还在不断地演进,持续推出更新的技术,以此推动Chiplet技术持续向前发展。

Chiplet对国内产业的意义与应用

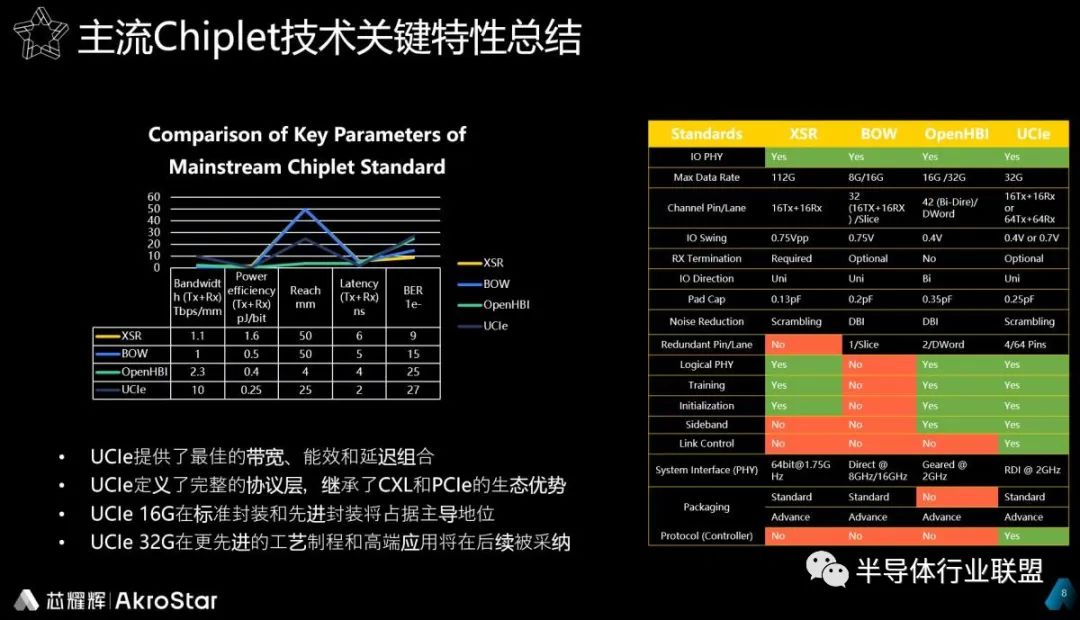

在单位硅片面积增加晶体管数量存在困难的情形下,国内芯片产业致力于在单个封装内部不断提升晶体管数量,此时发展Chiplet技术,其意义十分重大。

D2D IP解决方案和国内生产加工能力适配度很高,112G PAM4测试芯片已成功完成实测。芯耀辉从IP设计的源头出发,考虑Chiplet的要求,解决后端实现方面的挑战,为国内Chiplet技术发展提供了不错的范例。这会推动国内芯片产业更快地突破技术瓶颈,跟上国际的步伐。

大家都在想,Chiplet技术在未来能不能彻底解决芯片性能提升方面的难题?欢迎在评论区留言,同时也别忘了给本文点赞、分享!